Samsung to begin high-volume 3nm chip production for 2022

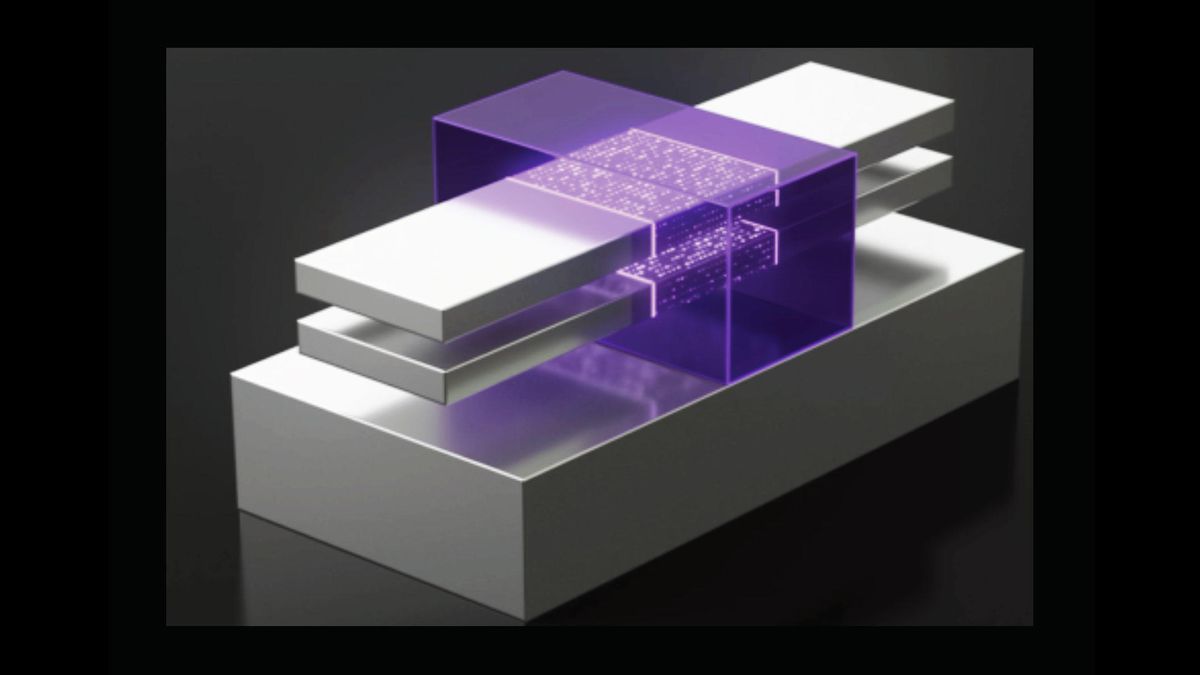

Samsung Foundry, the second-biggest independent foundry after TSMC, has rolled out certain improvements to its 3nm process node as indicated by AnandTech. The first chips from Samsung Foundry to be created utilizing the 3nm interaction, 3GAE (3nm Gate-All-Around Early), will allegedly be going through high-volume manufacturing a year after the fact than expected. It likewise was eliminated from Samsung’s roadmap showing that 3GAE may be produced for internal utilize as it were.

A Samsung delegate said, “As for the 3GAE process, we’ve been in discussion with customers and expect to mass-produce 3GAE in 2022.” 3GAE’s successor, the 3GAP (3nm Gate-All-Around Plus) hub actually is recorded on the guide with volume fabricating expected to start in 2023. The previously mentioned guide was disclosed at Foundry Forum 2021 in China. Samsung Foundry presented its refreshed tech guide which was then republished on Baidu and Weibo.

Concerning its chips utilizing the older FinFET transistor architecture, Samsung has added 5LPP, and 4LPP to its guide with high-volume producing set for 2021, and 2022, separately. At the point when Samsung disclosed its 3GAE and 3GAP hubs in May 2019, it declared that it’s anything but a 35% expansion in execution, a half decrease in power utilization contrasted with 7LPP which presently is the past generation process node.

Simultaneously back in 2019, volume-creation utilizing 3GAA (Gate-All-Around semiconductor engineering) was reported to begin in late 2021. With the new dispatch date of 2022 for the 3nm Gate-All-Around Early process, one can presume that there has been a slight postponement on Samsung’s part or an erroneous conclusion. In any case, it’s anything but viewed as nothing to joke about as Sammy’s Early hubs aren’t utilized by manufacturers generally.

Only a couple days prior, Samsung Foundry taped out a 3nm chip that utilizes its Gate-All-Around (GAA) semiconductor engineering. Taping out a chip is the last venture of its plan cycle bringing about one of two results: the chip configuration works or it doesn’t. On account of the last mentioned, a minor fix may be required or a total upgrade of the design is called for.